The Need for Continuing Education

During consulting assignments, I constantly see engineers struggle to achieve EMC compliance, either emissions or immunity. This not only includes regulatory approval and functionality but also managing an in-house system that may not have been designed to include EMC and safety approvals. They are left on their own to experiment using trail-and-error techniques because management refuses to spend a little amount of money by bringing in a consultant or to send their engineers to a training class on both theory and applied application engineering directly related to their work.

The more senior one is at in design engineering, such as digital circuitry and printed circuit board layout, there is the tendency to do things in a manner that is familiar to them. What has been known to work in the past no longer applies due to advances in semiconductor technology and speed of operation, along with required packaging in a lightweight plastic enclosure instead of metal box. Time, money and extended effort is required, sometimes now with several engineers instead of one to solve what is probably a simple design or layout problem. These problems may be easy to visualize not only on the actual printed circuit board itself but also by looking at a schematic to find a design flaw such as a resistor used instead of a ferrite bead. If one had knowledge related to advances in high-speed signal integrity along with design concerns, our job of achieving compliance becomes easier.

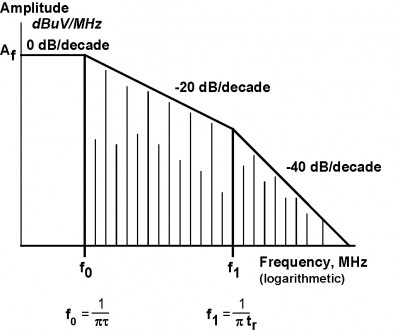

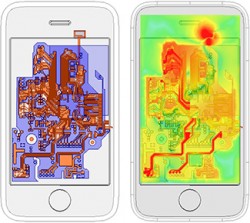

Most EMC engineers use only a spectrum analyzer to find problem areas on a PCB. After spending lots of time using a sniffer probe to locate where energy is coming from, if even successful, what do they do next? They now go again into a trial and error mode of trying fixing the problem. Whenever I get called to troubleshoot an EMI problem (frequency domain) as a consultant at the printed circuit board level, I use an oscilloscope to locate the source in the time domain. A spectrum analyzer only tells us there is an RF field present, not what created the undesired RF energy. RF energy is created due to losses within a transmission line, which is commonly referred to as a trace. It is impossible to isolate losses with a spectrum due to many second order effects that occur during layout on a physical structure; core and prepreg.

In order to understand advances in circuit analysis and transmission line theory, continued education is required. There are many places to learn that includes seminars (even at your own expense if the company does not want to pay), attendance at conferences, reading technical papers that are free on-line and networking with others. The manner in how you obtain continued education is up to you, as long as you stay current with technology and are willing to learn and accept new ideas that may sound bizarre. If you are not willing to pay for training out of your own pocket to ensure job security and to make your life easier at work with quicker success, then do you deserve to be employed by a company that is willing to replace you with someone else, usually at lower cost, to increase their revenue by not providing support to them employees such as continued education?

Advertisement: My company provide low-cost, professional training in all aspects of EMC design engineering based on EMC/EMI Made Simple as well as Maxwell Made Simple. All classes are taught at the fundamental level which provides significant value to even senior engineers to need to learn a new way of thinking about problems due to advances in technology with a focus on transmission line theory and its relationship to EMC.

Signal Integrity versus EMI

We need to maximize the functionality of a product using printed circuit boards while at the same time shrink the physical size along with lower cost of development and production. We are discovering that signal integrity is becoming a greater concern than EMC, especially at higher frequencies. Although a system may radiate undesired EMI in a broadband environment, will EMI be a concern in the future or should we enhance immunity protection against any and all electromagnetic threats that may occur at the microscopic level?

EMC engineers must understand multiple aspects of doing a printed circuit board layout in a manner that ensures not only functionality but also compliance. The magnitude of a signal integrity problem due to losses in a transmission line is the magnitude of undesired common-mode RF current that gets developed, and which will propagate through either radiated or conducted means. To reiterate, losses in a transmission line between source and receptor creates common-mode RF energy. It is easier to work in the time domain instead of the frequency domain when performing circuit analysis.

A transmission line, commonly called a trace on a PCB, propagates an electromagnetic field between locations. During propagation, there must be no loss in any parametric value of the signal if optimal signal integrity is to be ensured. Some parametric values include changes in voltage, current, propagation delay, timing, edge rate distortion, impedance discontinuities, and the like. If a transmission line is perfectly lossless we have optimal signal integrity and no EMI. To help minimize signal propagation loss, RF return current must be equal and opposite to the source transmission line. Thus, if there is any significant loss in either the source or return path, common-mode EMI is developed as this energy must still return to its source per Ampere’s law, except in an undesired transmission line path per Kirchhoff.

In the future, all engineers must understand the following sample list of signal integrity concerns, and there are many: Incorrect transmission line routing; improper terminations; power and/or return plane bounce; rise time degradation; lossy lines at higher frequencies due to board material usage; hidden parasitics (RLC); skin depth losses; dielectric loss in the board material; propagation delays due to high dielectric constant board material; crosstalk; excessive inductance in transmission line routing; delta I noise; overshoot and undershoot; IR drops; copper roughness; anisotropic aspects of the board material; and RoHS (affects delamination and may create tin whisker) to name a few parametric concerns. In essence, we can no longer consider only electromagnetic aspects of signal propagation in both the time and frequency domain, but must now become knowledgeable in material science to enhance signal integrity and minimize development of common-mode current.

Locating RF on a Printed Circuit Board

Why FR-4 is Obsolete for Tomorrow’s Technology

Many designers who create a printed circuit board, know little about the field of EMC. Why should they since at the physical level, why worry, EMC is an electrical issue and not mechanical or structural. For at least two generations, engineers will specify FR-4, because nothing else exist or they are unaware of what occurs in a physical design when using this material.

Management mandates FR-4 because of low cost. Fiberglass Resin (FR) has been used for decades so why change. There are however applications and usage beyond the world of FR-4 such as military, satellite applications, harsh environmental conditions and other unique environments of use. When using FR-4 in high frequency digital applications, should we be concerned more with electrical performance or low cost?

One reason why FR-4 is becoming obsolete for today’s products deals not only with dielectric loss but also weave density and layout of the fiberglass strands. There is also the RoHS (Restriction of Hazardous Substance) Directive in Europe, China and North America. The RoHS Directive makes the use of lead in any product illegal, which include a particular type of solder. Typical solder consists of PbSn (60% tin-40% lead). Since PbSn solder is now prohibited on a near world-wide basis, an alternative metallurgy material is now required which includes Nickel and other alloys. These alloys lead to microscopic problems known as “tin whiskers”, among other items. Over time, small metallic whiskers may grow from a soldered joint that could short out circuits causing system wide failure. NASA has significant documentation on tin whisker growth as well as the Raytheon Corporation. Another concern that is even greater why FR-4 is becoming obsolete for technologies of the future operating in the GHz range is that in order to use the new alloy of solder, higher processing temperatures are required to ensure melting during reflow. With higher process temperatures, the resin used to hold the fiberglass stands together will start to evaporate water in the resin and delamination of the copper from the fiberglass core occurs. We now a reliability concern.

Should we worry more about electrical performance for high technology products using FR-4, or just keep using low cost material because after all, quality with regard to functional operation is less important than cost?